# Low-Profile, 600mA, Synchronous Step-Down Converter with Integrated Inductor UM3502QA QFN24 4.0×4.0

## **General Description**

The UM3502QA is a complete power conversion solution requiring only two low cost ceramic MLCC caps. Inductor, MOSFETs, synchronous rectifier and control IC are integrated into a tiny 4mm×4mm×1.05mm QFN package. The UM3502QA is engineered to simplify design and to minimize layout constraints. It is an ideal choice to be used to replace less efficient LDO to achieve improved efficiency in space restricted applications. The UM3502QA is capable of delivering 600mA output current over a wide input voltage range from 2.5V to 5.5V.

The UM3502QA is a high-efficiency, step-down DC-DC converter with a constant PWM frequency, current mode architecture. The UM3502QA automatically turns off the synchronous rectifier while the inductor current is low, and enters pulse skipping mode at light load condition. This can increase efficiency. The operation frequency is set to 1.2MHz at normal load condition. The UM3502QA enters shutdown mode and consumes less than  $0.1\,\mu\text{A}$  when EN pin is pulled low.

## **Applications**

- Cellular and Smart Phones

- MCU, DSP and FPGA Core Supplies

- Wireless and DSL Modems

- Portable Game Consoles and Instruments

- PDAs, GPS

- Bluetooth Headsets

- Battery-Powered Devices

#### **Features**

- Ultra Small QFN Package 4.0×4.0×1.05

- Integrated Inductor

- No Schottky Diode Required

- High Efficiency: Up to 90%

- 600mA Output Current

- 0.6V Minimum Output Voltage

- 2.5V to 5.5V Input Voltage Range

- <1 µA Shutdown Current

- Pulse Skipping Mode Operation

- Thermal Fault Protection

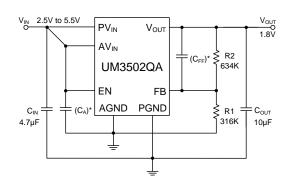

#### **Typical Application Circuit**

<sup>\*</sup> C<sub>A</sub> and C<sub>FF</sub> are optional.

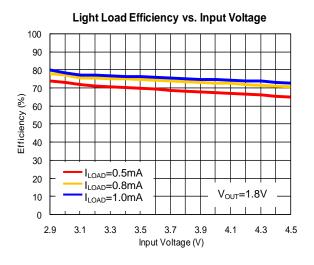

#### **Light Load Efficiency**

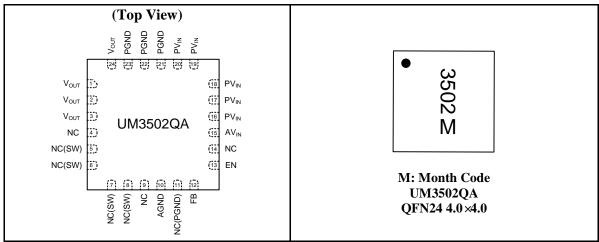

## **Pin Configurations**

## **Top View**

**Pin Description**

| Pin Number | Symbol                      | Function                                                                                                                                                                                                                                     |  |

|------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1-3, 24    | $ m V_{OUT}$                | Regulated output voltage. Must be closely placed a $10\mu F$ or greater ceramic capacitor. These pins are connected together inside the package.                                                                                             |  |

| 4, 9, 14   | NC                          | Not connected.                                                                                                                                                                                                                               |  |

| 5-8        | NC(SW)                      | Not connected—These pins are internally connected to the common switching node of the internal MOSFETs. NC(SW) pin are not to be electrically connected to any external signal, groun or voltage. However, they must be soldered to the PCB. |  |

| 10         | AGND                        | Analog ground. This is the ground for the internal control circuitry, and the ground return for external feedback voltage divider. It must be connected to the quiet point of the ground.                                                    |  |

| 21-23      | PGND                        | Power ground. Connect this pin to the ground electrode of the input and output filter capacitors closely.                                                                                                                                    |  |

| 11         | NC(PGND)                    | This pin has been connected with PGND inside the package. No other connection is needed in use.                                                                                                                                              |  |

| 12         | FB                          | Feedback input pin. Connect FB to the center point of the external resistor divider.                                                                                                                                                         |  |

| 13         | EN                          | Chip enable control. Drive EN above 1.0V to turn on the part. Drive EN below 0.4V to turn it off. Do not leave EN floating.                                                                                                                  |  |

| 15         | $\mathrm{AV}_{\mathrm{IN}}$ | Input power supply for the controller circuitry. Connect to $V_{\rm IN}$ at a quiet point. This pin is usually connected to the positive electrode of $C_{\rm IN}$ .                                                                         |  |

| 16-20      | $PV_{IN}$                   | Power input for the MOSFET switches. Must be clo decoupled to GND with a 4.7μF or greater ceramic capac These pins are connected together inside the package.                                                                                |  |

**Ordering Information**

| Part Number | Packaging Type | Marking Code | Shipping Qty                  |

|-------------|----------------|--------------|-------------------------------|

| UM3502QA    | QFN24 4.0×4.0  | 3502         | 3000pcs/13Inch<br>Tape & Reel |

**Absolute Maximum Ratings (Note 1)**

| Symbol                    | Parameter                                            | Value                        | Unit           |

|---------------------------|------------------------------------------------------|------------------------------|----------------|

| $V_{\rm IN}, V_{\rm OUT}$ | Input and Output Voltages                            | -0.3 to +6.0                 | V              |

| $V_{EN}, V_{FB}$          | V <sub>EN</sub> , V <sub>FB</sub> EN, FB Voltages    |                              | V              |

| $V_{\mathrm{sw}}$         | SW Voltage                                           | -0.3 to V <sub>IN</sub> +0.3 | V              |

| $I_{SW}$                  | I <sub>SW</sub> Peak SW Sink and Source Current      |                              | A              |

| To                        | Operating Temperature                                | -40 to +85                   | ${\mathbb C}$  |

| $T_{STG}$                 | Storage Temperature Range                            | -65 to +150                  | ${\mathbb C}$  |

| $T_{REFLOW}$              | Reflow Temperature,<br>MSL3 JEDEC J-STD-020C, 10 Sec | 260                          | ${\mathcal C}$ |

Note 1: Stresses greater than those listed under Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Electrical Characteristics (Note 2)**

$(V_{IN}=V_{EN}=3.6V, T_A=+25 \, ^{\circ}C, C_{IN}=4.7 \mu F, C_{OUT}=10 \mu F, unless otherwise noted)$

| Symbol                    | Parameter                               | Test Conditions                                                              | Min    | Тур    | Max    | Unit |

|---------------------------|-----------------------------------------|------------------------------------------------------------------------------|--------|--------|--------|------|

| V <sub>IN</sub>           | Input Voltage Range                     |                                                                              | 2.5    |        | 5.5    | V    |

| V <sub>OUT</sub>          | Output Voltage Range                    |                                                                              | 0.6    |        | 5      | V    |

| T                         | M. i. O. i. G.                          | V <sub>IN</sub> ≥3V, V <sub>OUT</sub> =1.8V                                  | 600    |        |        | mA   |

| $I_{O(max)}$              | Maximum Output Current                  | V <sub>IN</sub> =2.5V, V <sub>OUT</sub> =1.8V                                | 300    |        |        |      |

| I <sub>Q</sub> (Active)   | Input DC Supply Current (Active Mode)   | V <sub>FB</sub> =0.6V, I <sub>LOAD</sub> =0A                                 |        | 60     |        | μΑ   |

| I <sub>Q</sub> (Shutdown) | Input DC Supply Current (Shutdown Mode) | $V_{EN}=0V$                                                                  |        | 0.1    | 1.0    | μΑ   |

| V                         | Foodback Voltage                        |                                                                              | 0.5880 | 0.6000 | 0.6120 | W    |

| $V_{ m FB}$               | Feedback Voltage                        | T <sub>A</sub> =-40~85 ℃                                                     | 0.5830 | 0.6000 | 0.6150 | V    |

| $I_{\mathrm{FB}}$         | FB Input Bias Current                   | $V_{FB} = 0.65 V$                                                            |        |        | ±30    | nA   |

|                           | Reference Voltage Line<br>Regulation    | $2.5V \le V_{IN} \le 5.5V,$<br>$V_{OUT} = V_{FB} (R2 = 0)$                   |        | 0.11   | 0.40   | %/V  |

|                           | Output Voltage Line<br>Regulation       | $ 2.5V \le V_{IN} \le 5.5V, $ $I_{OUT} = 10mA $                              |        | 0.11   | 0.40   | %/V  |

|                           | Output Voltage Load<br>Regulation       | 100mA≤I <sub>OUT</sub> ≤600mA                                                |        | 0.0015 |        | %/mA |

| f                         | Oscillator Frequency                    | $V_{FB}$ =0.6V or $V_{OUT}$ =100%                                            |        | 1.2    |        | MHz  |

| D                         | $R_{DS(ON)}$ of P-CH MOSFET             | V <sub>IN</sub> =3.6V,<br>I <sub>SW</sub> =100mA                             |        | 0.45   | 0.55   | Ω    |

| $R_{DS(ON)}$              | R <sub>DS(ON)</sub> of N-CH MOSFET      | V <sub>IN</sub> =3.6V,<br>I <sub>SW</sub> =-100mA                            |        | 0.30   | 0.40   | Ω    |

|                           | Internal Inductor DCR                   |                                                                              |        | 0.18   | 0.23   | Ω    |

| $I_P$                     | Peak Inductor Current                   | $V_{\rm IN}$ =3.0V, $V_{\rm FB}$ =0.5V or $V_{\rm OUT}$ =90%, Duty Cycle<35% | 0.90   | 1.20   | 1.60   | A    |

#### **Electrical Characteristics (Continued)**

$(V_{IN}=V_{EN}=3.6V, T_A=+25 \, ^{\circ}C, C_{IN}=4.7 \mu F, C_{OUT}=10 \mu F, unless otherwise noted)$

| Symbol           | Parameter                              | Test Conditions                                | Min | Тур   | Max | Unit |

|------------------|----------------------------------------|------------------------------------------------|-----|-------|-----|------|

| $I_{SWL}$        | SW Leakage                             | $V_{EN}$ =0V, $V_{IN}$ =5V, $V_{SW}$ =0V or 5V |     | ±0.01 | ±1  | μΑ   |

| $V_{\mathrm{H}}$ | EN High-Level<br>Threshold             | -40 ℃≤T <sub>A</sub> ≤85 ℃                     | 1.0 |       |     | V    |

| $V_{L}$          | EN Low-Level<br>Threshold              | -40 ℃≤T <sub>A</sub> ≤85°C                     |     |       | 0.4 | V    |

| $I_{ENL}$        | EN Leakage Current                     |                                                |     | ±0.1  | ±1  | μΑ   |

| $\eta_{(max)}$   | Max. Efficiency                        | $V_{IN}=3.6V, V_{OUT}=2.5V$                    |     | 90    |     | %    |

|                  | Thermal Shutdown Temperature           |                                                |     | 160   |     | C    |

|                  | Thermal Shutdown Trip Point Hysteresis |                                                |     | 25    |     | C    |

Note2: 100% production test at +25 °C. Specifications over the temperature range are guaranteed by design and characterization.

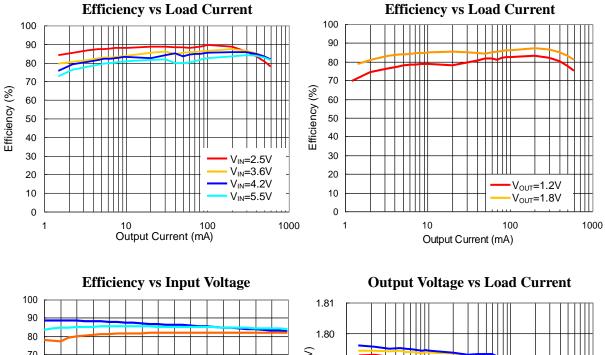

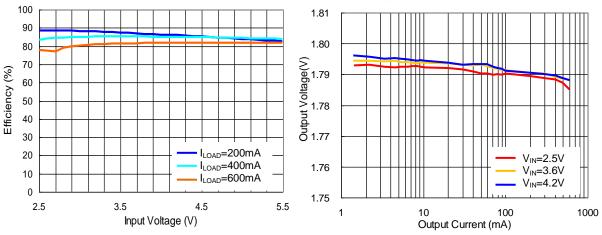

### **Typical Performance Characteristics**

$(V_{IN}=3.6V, V_{OUT}=1.8V, C_{IN}=4.7\mu F, C_{OUT}=10\mu F, T_A=+25 \, ^{\circ}C, unless otherwise noted.)$

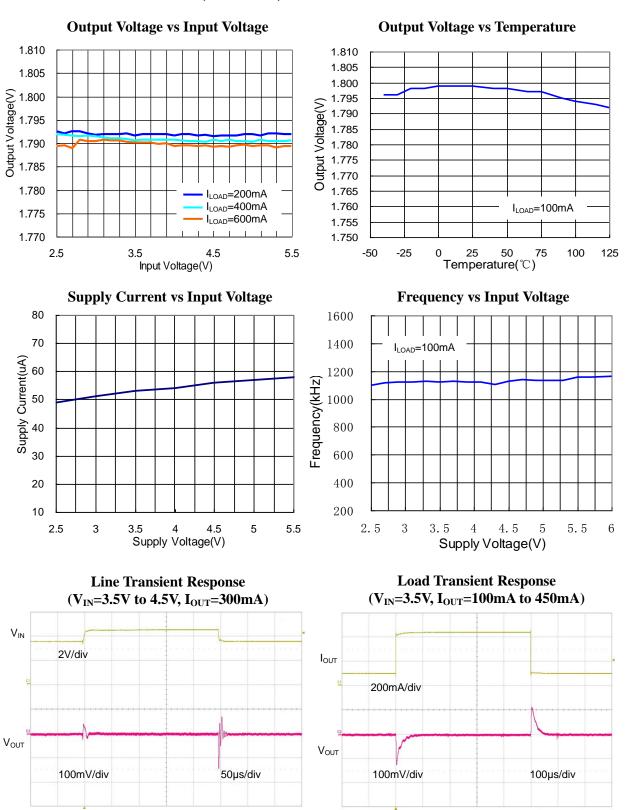

## **Typical Performance Characteristics (Continued)**

$(V_{IN}=3.6V, V_{OUT}=1.8V, C_{IN}=4.7\mu F, C_{OUT}=10\mu F, T_A=+25 \, \text{°C}, unless otherwise noted.})$

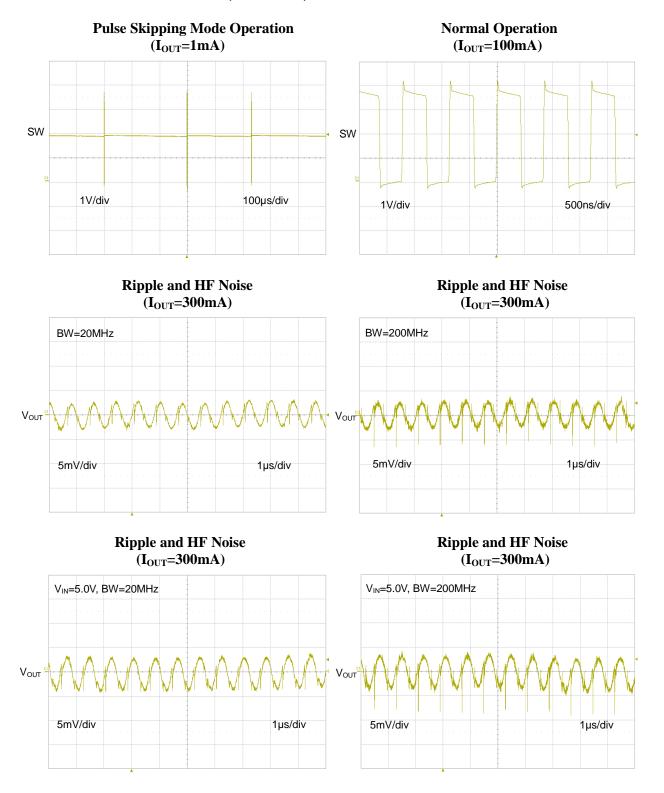

## **Typical Performance Characteristics (Continued)**

$(V_{IN}=3.6V, V_{OUT}=1.8V, C_{IN}=4.7\mu F, C_{OUT}=10\mu F, T_A=+25 \, ^{\circ}C, unless otherwise noted.)$

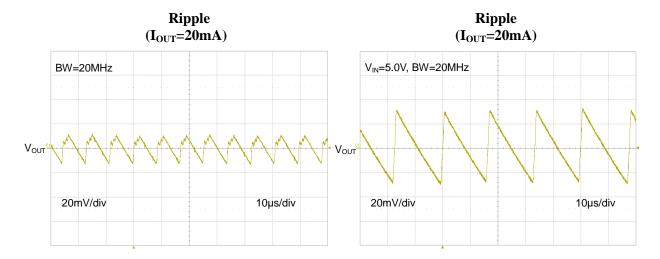

## **Typical Performance Characteristics (Continued)**

$(V_{IN}=3.6V, V_{OUT}=1.8V, C_{IN}=4.7\mu F, C_{OUT}=10\mu F, T_A=+25 \, ^{\circ}C$ , unless otherwise noted.)

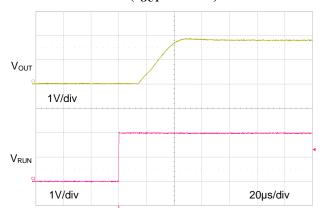

# $\begin{array}{c} Start\text{-up from Shutdown} \\ (I_{OUT}\text{=}300mA) \end{array}$

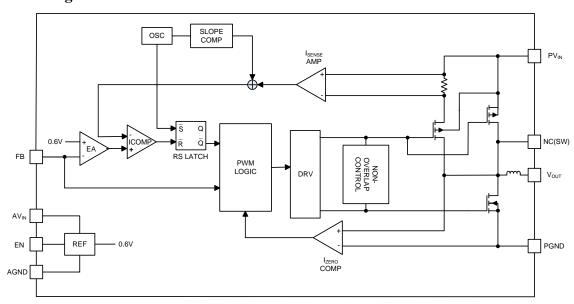

## **Block Diagram**

#### **Function Description**

#### **Integrated Inductor**

The UM3502QA utilizes a low loss, multilayer inductor. The DCR of the integrated inductor is  $180m\Omega$  and the inductor is about  $2.2\,\mu\text{H}$ . The use of an internal inductor localizes the noise associated with the output loop currents. The proprietary integrated inductor construction reduces the area of the converter's large current loop that can reduce the radiated noise coupled into the traces of the circuit board. Furthermore, the package layout is optimized to reduce the electrical path length for the AC ripple currents that are a major source of radiated emissions from DC-DC converters. The integrated inductor significantly reduces parasitic effects that can harm loop stability, and makes layout very simple. All these lead to lower output noise and fewer influences on the input power.

#### **Current Mode PWM Control and Current Limit**

The UM3502QA uses constant frequency, current mode step-down architecture. Both the main (P-channel MOSFET) and synchronous (N-channel MOSFET) switches are internal. From the block diagram, a comparator ICOMP is used to realize current limit protection. Lossless current sensing converts the peak current signal to a voltage to sum in with the internal slope compensation. This summed signal is compared to the error amplifier output to provide a peak current control command for the PWM. The cycle-by-cycle current limit is set at 1200mA (typical). During normal operation, the internal top power MOSFET is turned on each cycle when the oscillator sets the RS latch, and turned off when the current comparator ICOMP, resets the RS latch. The peak inductor current at which ICOMP resets the RS latch, is controlled by the output of error amplifier EA. When the load current increases, it causes a slight decrease in the feedback voltage, FB, relative to the 0.6V reference, which in turn, causes the EA amplifier's output voltage to increase until the average inductor current matches the new load current. While the top MOSFET is off, the bottom MOSFET is turned on until either the inductor current starts to reverse, as indicated by the current reversal comparator I<sub>ZERO</sub>, or the beginning of the next clock cycle.

When the output is shorted to ground, the inductor current may exceed the maximum inductor peak current if not allowed enough time to decay. To prevent the inductor current from running away, the bottom N-channel MOSFET is allowed to stay on for more than one cycle, thereby allowing the inductor current time to decay.

#### **Pulse Skipping Mode Operation**

At very light loads, the UM3502QA automatically enters Pulse Skipping Mode. In the Pulse Skipping Mode, the inductor current may reach zero or reverse on each pulse. The PWM control loop will automatically skip pulses to maintain output regulation. The bottom MOSFET is turned off by the current reversal comparator,  $I_{ZERO}$ , and the switch voltage will ring. This is discontinuous mode operation, and is normal behavior for the switching regulator.

#### **Enable**

The EN pin provides a means to shut down the converter or enable normal operation. A logic low will disable the converter and cause it to shut down. A logic high will enable the converter into normal operation. In shutdown mode, the device quiescent current will be less than  $1\mu A$ . The EN pin must not be left floating.

#### **Thermal Shutdown**

When excessive power is dissipated in the chip, the junction temperature rises. Once the junction temperature exceeds the thermal shutdown temperature, the thermal shutdown circuit turns off the converter output voltage thus allowing the device to cool. When the junction temperature decreases by  $25 \, ^{\circ}$ C, the device will go through the normal startup process.

#### **Applications Information**

#### **Output Voltage Setting**

The output voltage is set by a resistive divider according to the following formula:

$$V_{OUT} = 0.6 \text{V} \left( 1 + \frac{R2}{R1} \right)$$

The value of R1 should be less than  $500k\Omega$ , so that the input current on FB pin can reduce its influence on the accuracy of the output voltage. The  $C_{FF}$  capacitor is used to compensate the gain of the loop for improved stability and the value of the capacitor is usually 4.7pF to 22pF, but it is optional.

#### **Capacitor Selection**

The input capacitor reduces the surge current drawn from the input and switching noise from the device. The input capacitor impedance at the switching frequency shall be less than input source impedance to prevent high frequency switching current passing to the input. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a 4.7 µF capacitor is sufficient.

The  $AV_{IN}$  is separate from the  $PV_{IN}$  in the chip. A  $C_A$  capacitor can be used to decouple alone. The  $AV_{IN}$  can also be directly connected to the positive electrode of the  $C_{IN}$  to decouple.

The output capacitor keeps output voltage ripple small and ensures regulation loop stable. The output capacitor impedance shall be low at the switching frequency. Ceramic capacitor with X5R or X7R dielectrics are recommended. For most applications, a 10 µF capacitor is sufficient. For smaller output voltage ripple, you can choose a bigger output capacitor.

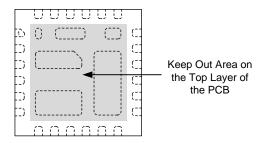

#### **Exposed Metal on the Bottom of the Package**

The UM3502QA utilizes the lead frame as part of the electrical circuit. The lead frame offers many advantages in thermal performance, in reduced electrical lead resistance and in overall foot print. However, it does require some special considerations.

As part of the package assembly process, lead frame construction requires that for mechanical support, some of the lead-frame metal be exposed at the point where wire-bond or internal passives are attached. This results in several small pads being exposed on the bottom of the package.

The "grayed-out" area in Figure 1 represents the area that should be clear of any metal (traces, vias, or planes) on the top layer of the PCB.

Figure 1. Exposed Metal of the Package

#### **Layout Guidance**

The package of the UM3502QA has been optimized that makes it easy for layout. It is an ideal choice to be used to replace less efficient LDO to achieve improved efficiency in space restricted applications.

When laying out the PC board, the following suggestions should be taken to ensure higher performance of the UM3502QA.

- 1. PCB with at least two planes is recommended. Keep the GND plane under the converter as complete as possible.

- 2. Connect the input capacitor  $C_{IN}$  to the  $PV_{IN}$  and PGND pins, the output capacitor  $C_{OUT}$  to the  $V_{OUT}$  and PGND pins as closely as possible to get good power filter effect.

- 3. The power traces, including the PGND trace, the  $PV_{IN}$  trace and  $V_{OUT}$  trace should be kept short, direct and wide to allow large current flow.

- 4. Connect  $AV_{IN}$  and AGND to a quiet point. The AGND pin is usually connected to the GND plane by vias. The  $AV_{IN}$  pin should be directly connected to the positive electrode of  $C_{IN}$ . A  $0.1\,\mu\text{F}$  capacitor can also be used to decouple for better performance.

- 5. Keep the SW pin away from the sensitive FB node. This pin should also not be electrically connected to any external signal, ground, or voltage.

- 6. Do not trace signal line under the chip.

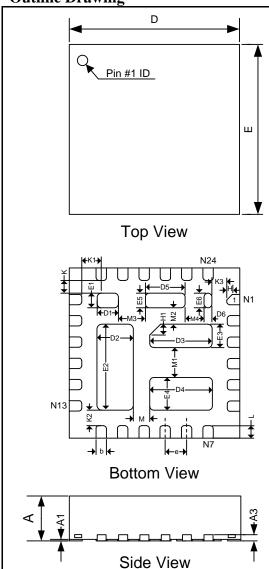

# **Package Information**

UM3502QA: QFN24 4.0×4.0

**Outline Drawing**

| DIMENGIONG             |      |                  |      |  |  |

|------------------------|------|------------------|------|--|--|

| DIMENSIONS MILLIMETERS |      |                  |      |  |  |

| Symbol                 | Min  | Typ              | Max  |  |  |

| A                      | 1.00 | 1.05             | 1.10 |  |  |

| A1                     | 0.00 | 0.02             | 0.05 |  |  |

| A3                     | 0.00 | 0.02<br>0.152REF | 0.03 |  |  |

| b                      | 0.20 | 0.132KL1         | 0.30 |  |  |

| D                      | 3.90 | 4.00             | 4.10 |  |  |

| E                      | 3.90 | 4.00             | 4.10 |  |  |

| D1                     | 0.40 | 0.50             | 0.60 |  |  |

| E1                     | 0.25 | 0.35             | 0.45 |  |  |

| D2                     | 0.75 | 0.85             | 0.45 |  |  |

| E2                     | 1.92 | 2.02             | 2.12 |  |  |

| D3                     | 1.37 | 1.47             | 1.57 |  |  |

| E3                     | 0.45 | 0.55             | 0.65 |  |  |

| D4                     | 1.37 | 1.47             | 1.57 |  |  |

| E4                     | 0.67 | 0.77             | 0.87 |  |  |

| D5                     | 0.84 | 0.94             | 1.04 |  |  |

| E5                     | 0.25 | 0.35             | 0.45 |  |  |

| D6                     | 0.10 | 0.20             | 0.30 |  |  |

| E6                     | 0.25 | 0.35             | 0.45 |  |  |

| e                      | 0.40 | 0.50             | 0.60 |  |  |

| Н                      | 0.40 | 0.125REF         | 0.00 |  |  |

| H1                     |      | 0.25REF          |      |  |  |

| K                      | 0.20 | 0.30             | 0.40 |  |  |

| K1                     | 0.25 | 0.35             | 0.45 |  |  |

| K2                     | 0.25 | 0.35             | 0.45 |  |  |

| K3                     | 0.25 | 0.35             | 0.45 |  |  |

| L                      | 0.25 | 0.30             | 0.35 |  |  |

| M                      | 0.28 | 0.38             | 0.48 |  |  |

| M1                     | 0.60 | 0.70             | 0.80 |  |  |

| M2                     | 0.28 | 0.38             | 0.48 |  |  |

| M3                     | 0.53 | 0.63             | 0.73 |  |  |

| M4                     | 0.33 | 0.43             | 0.53 |  |  |

|                        |      | ~···             |      |  |  |

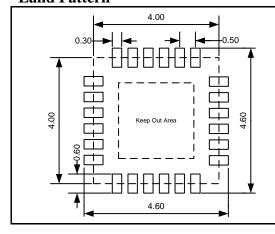

## **Land Pattern**

#### NOTES:

- 1. Compound dimension: 4.00×4.00;

- 2. Unit: mm;

- 3. General tolerance ±0.05mm unless otherwise specified;

- 4. The layout is just for reference.

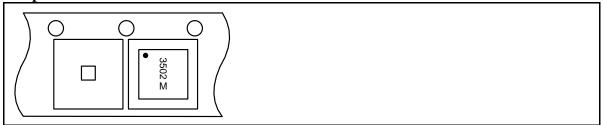

**Tape and Reel Orientation**

### **GREEN COMPLIANCE**

Union Semiconductor is committed to environmental excellence in all aspects of its operations including meeting or exceeding regulatory requirements with respect to the use of hazardous substances. Numerous successful programs have been implemented to reduce the use of hazardous substances and/or emissions.

All Union components are compliant with the RoHS directive, which helps to support customers in their compliance with environmental directives. For more green compliance information, please visit:

http://www.union-ic.com/index.aspx?cat\_code=RoHSDeclaration

#### IMPORTANT NOTICE

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Union assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any update. Union reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.

Union Semiconductor, Inc

Add: Unit 606, No.570 Shengxia Road, Shanghai 201210

Tel: 021-51093966 Fax: 021-51026018

Website: www.union-ic.com